眨眼间能完成10亿次存储,上海科研团队研制出超高速闪存

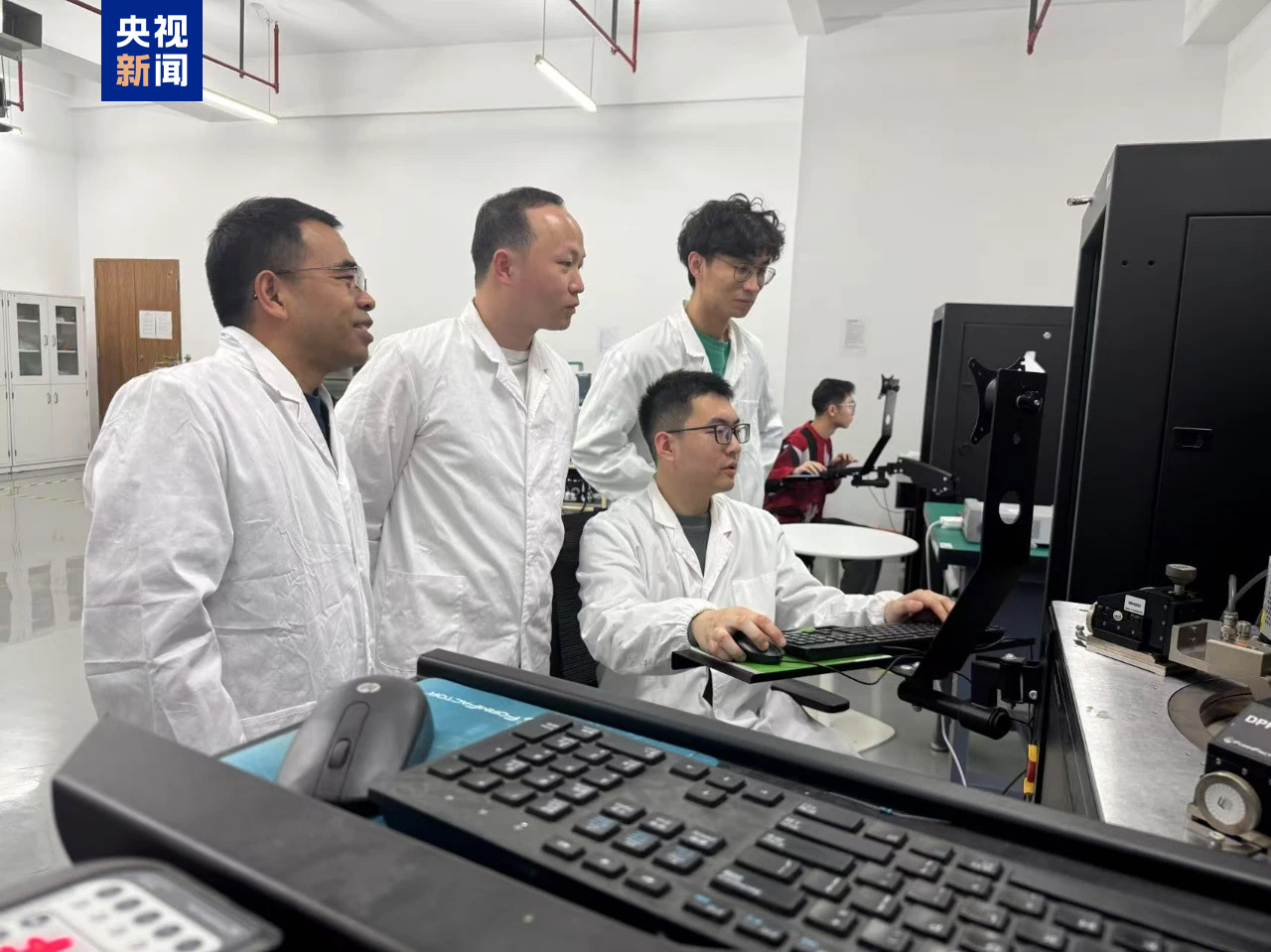

记者从上海市科委获悉,集成芯片与系统全国重点实验室周鹏-刘春森团队通过构建准二维泊松模型在理论上,预测了超注入现象打破了现有存储速度的理论极限研制“破晓(PoX)”皮秒闪存器件。其擦写速度可提升至亚1纳秒。400皮秒相当于每秒可执行25亿次操作,是迄今为止世界上最快的半导体电荷存储技术。相关成果以《亚纳秒超注入闪存》为题于北京时间4月16日晚间在《自然》(Nature)期刊上发表。

AI时代,大数据的高速存储至关重要。如何突破信息存储速度极限,一直是集成电路领域最核心的基础性问题之一,也是制约AI算力上限的关键技术瓶颈。要实现大数据的高速存储,意味着与之匹配的存储器必须是在存储速度、能耗、容量上均表现优异的“六边形战士”。

然而,既有存储器的速度分级架构形如一座金字塔——位于塔上层的易失性存储器(如SRAM、DRAM)拥有纳秒级的高速存储,但其存储容量小、功耗大、制造成本高、断电后数据会丢失;而位于塔底的非易失性存储器(如闪存)则恰恰相反,虽克服了前者的种种劣势,但唯一的美中不足,便是百微秒级的存取速度不及前者十万分之一,遑论满足AI的计算需求。

既然闪存除了速度都是优点,有没有可能补齐它的速度短板?为此,周鹏-刘春森团队开展攻关,试图重新定义存储的边界,找到一种“完美”的存储器。

作为闪存的基本存储单元,浮栅晶体管由源极、漏极和栅极所组成。当电子从源极顺着沟道“跑”向漏极的过程中,按下栅极这一“开关”,电子便可被拽入浮栅存储层,实现信息存储。

“过去为闪存提速的思路,是让电子在跑道上先热身加速一段时间,等具备了高能量再按下开关。”刘春森形象解释。但在传统理论机制下,电子的“助跑”距离长、提速慢,半导体特殊的电场分布也决定了电子加速存在理论上限,令闪存存储速度无法突破注入极值点。

从存储器件的底层理论机制出发,团队提出了一条全新的提速思路——通过结合二维狄拉克能带结构与弹道输运特性,调制二维沟道的高斯长度,从而实现沟道电荷向浮栅存储层的超注入。在超注入机制下,电子无需“助跑”就可以直接提至高速,而且可以无限注入,不再受注入极值点的限制。

通过构建准二维泊松模型,团队成功在理论上预测了超注入现象,据此研制的皮秒闪存器件擦写速度闯入亚1纳秒大关(400皮秒),相当于每秒可执行25亿次操作,性能超越同技术节点下世界最快的易失性存储SRAM技术。

这是迄今为止世界上最快的半导体电荷存储技术,实现了存储、计算速度相当,在完成规模化集成后有望彻底颠覆现有的存储器架构。在该技术基础上,未来的个人电脑将不存在内存和外存的概念,无需分层存储,还能实现AI大模型的本地部署。

作为智能时代的核心基座,存储技术的速度边界拓宽或将引发应用场景指数级的革新,并成为我国在人工智能、云计算、通信工程等相关领域实现技术引领的“底气”之一。下一步,他们计划在3~5年将其集成到几十兆的水平,届时可授权给企业进行产业化。

据悉,该全国重点实验室依托复旦大学建设,周鹏和刘春森均是实验室骨干成员。此研究工作得到了科技部重点研发计划、国家自然科学基金人才类项目、上海市基础研究相关项目支持,以及教育部创新平台的支持。

相关文章

是什么,坚定了外资企业“在浦东为世界”的决心?

对话|女足国脚,离开体制“再就业”

非盟特别会议聚焦美国关税政策,共商应对之法

“努力稳住外贸基本盘”,浙江省委书记、省长接连调研外贸

美联储主席警告关税影响,纳指跌超3%,黄金续创历史新高

上海:文旅资源全面对接老年人需求,创新“银发伴旅”服务

奥园集团:截至3月底逾期债务约438.33亿元

丝路枢纽“扩容”,乌鲁木齐天山国际机场启用新航站楼

上海铁三浓度越来越高,长三角国际铁人三项赛下月开赛

OpenAI推出全新推理模型o3、o4-mini,以及一个编程智能体

美联储主席:特朗普关税政策导致的通胀上升影响可能更加持久,不会干预美国股市

世界银行行长:不确定性将导致全球经济增长低于预期

世贸组织:美关税政策致全球贸易前景严重恶化

亚马逊云:中国企业开始以“行业集群”的方式出海

首批换药患者已出现,两大减肥药巨头比拼的是什么?

体坛联播|阿森纳、国米晋级欧冠半决赛,王楚钦晋级16强

女子称收养女婴10年仍是“黑户”,河北武安:待查明弃婴来源后按程序办理

信心从何而来|楼市回稳的最新迹象

四川内江市市中区发生3.8级地震,震源深度10千米

- 2024年沪市REITs实际分红近60亿,高速公路REITs占半壁江山

- 沪克航旅推介会举行,年底前东航将开通上海-克拉玛依直达航班

- 突破3270美元关口!现货黄金再创新高,日内涨超40美元

- 王嘉评《在机器的边界思考》|一种宇宙技术的思考

- 马上评|上海市领导调研外贸外资企业,为何强调这三句话

- 网文书单|女频网文只是过家家?姐姐们搞事业干得飞起

- 伊朗外长: 下一轮伊美核问题谈判将于26日举行

- 对话|棋后居文君:创造历史之后,还有继续追梦的心

- 韩国一战机飞行训练中掉落机炮吊舱和空油箱

- 观察|中日航线加速扩容,航空公司如何抓住机会?

- 85岁眼科专家、武汉大学人民医院原眼科主任喻长泰逝世

- 解除近70家煤电厂有毒物质排放限制,特朗普能重振煤炭吗?